FiO 2

Quick Overview

• Based on ARM Cortex-M4 STM32F417IG MCU

• All IO pins available via pin headers upto 140 pins

• Pin compatible with STM32F4DISCOVERY board

• Onboard 8MHz crystal (for HSE clock)

• JTAG Debugger port

• Require ST-Link to program and debug

• Optional External SDRAM (up to 512 kBytes)

• Optional Onboard 32.768kHz crystal (for real time clock) with button (2032) battery holder

**IMPORTANT NOTE**: FiO 2 requires ST Link to program the MCU.

Supported Matlab / Simulink Software (Waijung Blockset)

Tutorials:

• FiO2 and aMG Labkit – Blinky demo

• Other tutorials

SKU

aMG_P004

Out of stock

SKU

aMG_P004

฿2,000.00

STM32F417IG Features

Core: ARM 32-bit Cortex™-M4 CPU with Floating Point Unit, Adaptive real-time accelerator (ART Accelerator™) allowing 0-wait state execution from Flash memory, frequency up to 168 MHz, memory protection unit, 210 DMIPS/1.25 DMIPS/MHz (Dhrystone 2.1), and DSP instructions• Memories

– Up to 1 Mbyte of Flash memory

– Up to 192+4 Kbytes of SRAM including 64-Kbyte of CCM (core coupled memory) data RAM

– Flexible static memory controller supporting Compact Flash, SRAM, PSRAM, NOR and NAND memories

• LCD parallel interface, 8080/6800 modes

• Clock, reset and supply management

– 1.8 V to 3.6 V application supply and I/Os

– POR, PDR, PVD and BOR

– 4-to-26 MHz crystal oscillator

– Internal 16 MHz factory-trimmed RC (1% accuracy)

– 32 kHz oscillator for RTC with calibration

– Internal 32 kHz RC with calibration

• Low power

– Sleep, Stop and Standby modes

– VBAT supply for RTC, 20×32 bit backup registers + optional 4 KB backup SRAM

• 3×12-bit, 2.4 MSPS A/D converters: up to 24 channels and 7.2 MSPS in triple interleaved mode

• 2×12-bit D/A converters

• General-purpose DMA: 16-stream DMA controller with FIFOs and burst support

• Up to 17 timers: up to twelve 16-bit and two 32-bit timers up to 168 MHz, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

• Debug mode – Serial wire debug (SWD) & JTAG interfaces – Cortex-M4 Embedded Trace Macrocell™

• Up to 140 I/O ports with interrupt capability – Up to 136 fast I/Os up to 84 MHz – Up to 138 5 V-tolerant I/Os

• Up to 15 communication interfaces

– Up to 3 × I2C interfaces (SMBus/PMBus)

– Up to 4 USARTs/2 UARTs (10.5 Mbit/s, ISO 7816 interface, LIN, IrDA, modem control)

– Up to 3 SPIs (37.5 Mbits/s), 2 with muxed full-duplex I2S to achieve audio class accuracy via internal audio PLL or external clock

– 2 × CAN interfaces (2.0B Active)

– SDIO interface

• Advanced connectivity

– USB 2.0 full-speed device/host/OTG controller with on-chip PHY

– USB 2.0 high-speed/full-speed device/host/OTG controller with dedicated DMA, on-chip full-speed PHY and ULPI

• 8- to 14-bit parallel camera interface up to 54 Mbytes/s

• Cryptographic acceleration: hardware acceleration for AES 128, 192, 256, Triple DES, HASH (MD5, SHA-1), and HMAC

• True random number generator

• CRC calculation unit

• 96-bit unique ID

• RTC: subsecond accuracy, hardware calendar

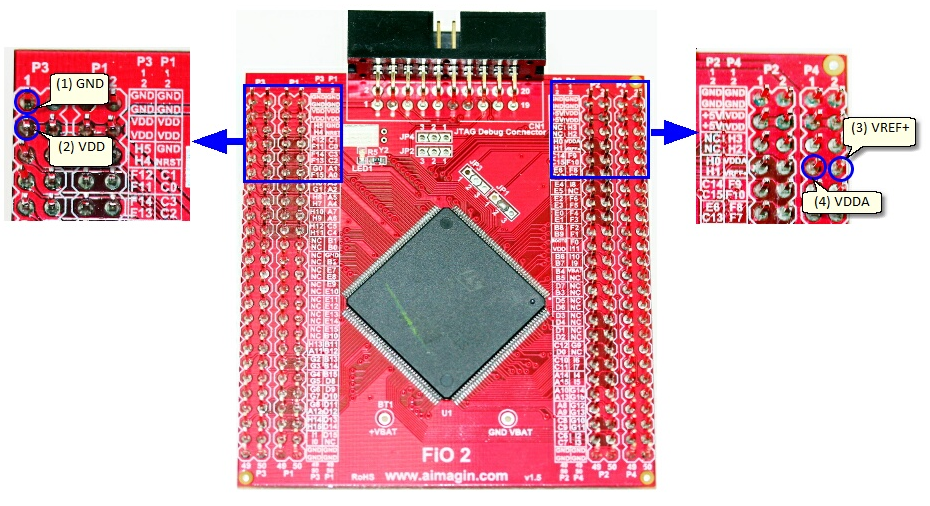

FiO 2 has been designed to be pin compatible with STM32F4DISCOVERY and fully compatible with aMG F4 Connect 2. If you plan to use FiO 2 without aMG F4 Connect 2, the following picture show minimum required connections.

1. Connect GND to connector P3, pin

2. Connect VDD (3.3V @HCLK=168MHz) to connector P3, pin 3.

3. Connect VREF+ to VDD (3.3V).

4. Connect VDDA to VDD (3.3V)

All VDD and GND on FiO 2 are connected together by designed and are intended for better distribution of VDD and GND.

Write Your Own Review